Image shown is a representation only.

Exact specifications should be obtained from the product data sheet.

Professional supply Integrated circuit IC one-stop sercvice BOM 8A34001E-000AJG Clock Synchronizer IC 1GHz 8 144-TFBGA

Clock Synthesizer / Jitter Cleaner 8A34001E-000 SYNCHRONIZATION MANAGEMENT UNIT

Product Descriptions

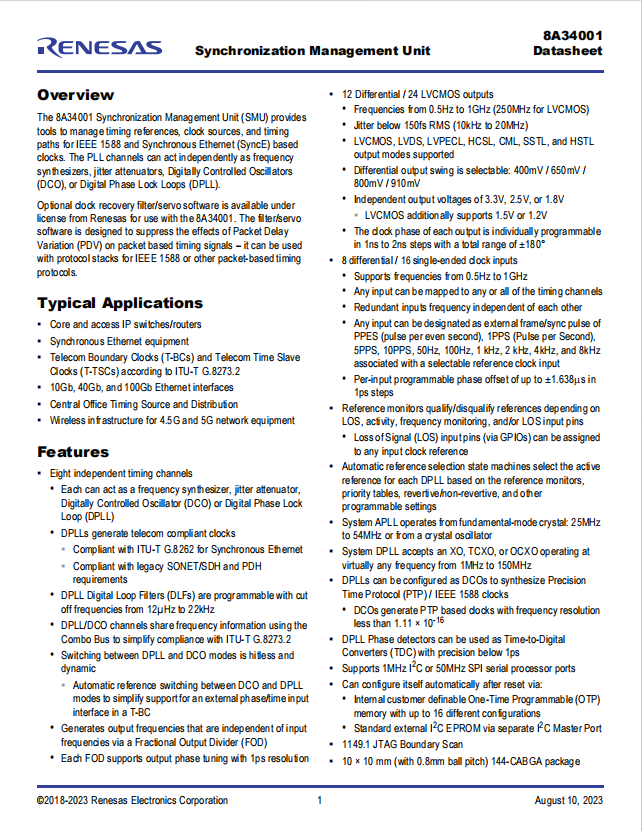

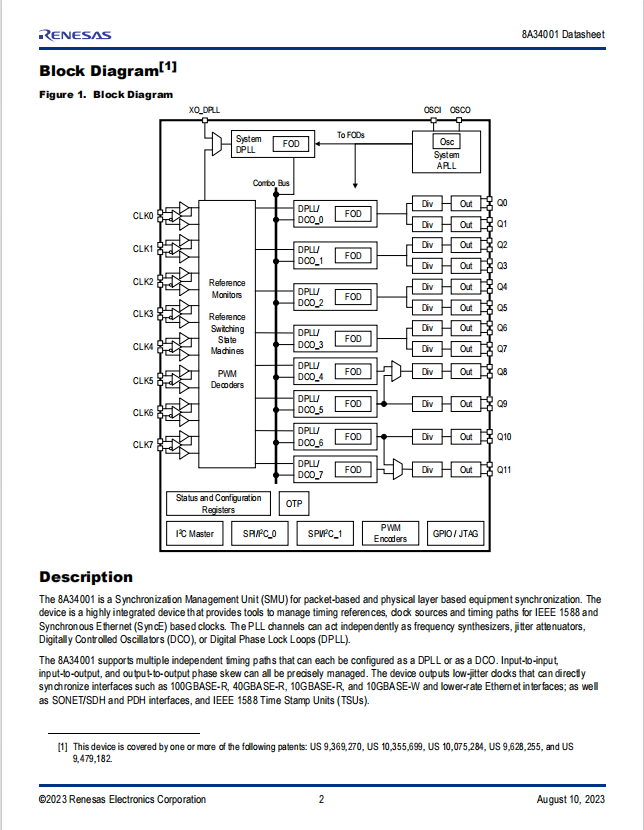

The 8A34001 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources, and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The PLL channels can act independently as frequency synthesizers, jitter attenuators, Digitally Controlled Oscillators (DCO), or Digital Phase Lock Loops (DPLL). Optional clock recovery filter/servo software is available under license from Renesas for use with the 8A34001. The filter/servo software is designed to suppress the effects of Packet Delay Variation (PDV) on packet based timing signals – it can be used with protocol stacks for IEEE 1588 or other packet-based timing protocols.

Product Typical Applications

▪ Core and access IP switches/routers

▪ Synchronous Ethernet equipment

▪ Telecom Boundary Clocks (T-BCs) and Telecom Time Slave Clocks (T-TSCs) according to ITU-T G.8273.2

▪ 10Gb, 40Gb, and 100Gb Ethernet interfaces

▪ Central Office Timing Source and Distribution

▪ Wireless infrastructure for 4.5G and 5G network equipment

Product Features

▪ Eight independent timing channels

• Each can act as a frequency synthesizer, jitter attenuator, Digitally Controlled Oscillator (DCO) or Digital Phase Lock Loop (DPLL)

• DPLLs generate telecom compliant clocks

▪ Compliant with ITU-T G.8262 for Synchronous Ethernet

▪ Compliant with legacy SONET/SDH and PDH requirements

• DPLL Digital Loop Filters (DLFs) are programmable with cut off frequencies from 12µHz to 22kHz

• DPLL/DCO channels share frequency information using the Combo Bus to simplify compliance with ITU-T G.8273.2

• Switching between DPLL and DCO modes is hitless and dynamic

▪ Automatic reference switching between DCO and DPLL modes to simplify support for an external phase/time input interface in a T-BC

• Generates output frequencies that are independent of input frequencies via a Fractional Output Divider (FOD)

• Each FOD supports output phase tuning with 1ps resolution

▪ 12 Differential / 24 LVCMOS outputs

• Frequencies from 0.5Hz to 1GHz (250MHz for LVCMOS)

• Jitter below 150fs RMS (10kHz to 20MHz)

• LVCMOS, LVDS, LVPECL, HCSL, CML, SSTL, and HSTL output modes supported

• Differential output swing is selectable: 400mV / 650mV / 800mV / 910mV

• Independent output voltages of 3.3V, 2.5V, or 1.8V

▪ LVCMOS additionally supports 1.5V or 1.2V

• The clock phase of each output is individually programmable in 1ns to 2ns steps with a total range of ±180°

▪ 8 differential / 16 single-ended clock inputs

• Supports frequencies from 0.5Hz to 1GHz

• Any input can be mapped to any or all of the timing channels

• Redundant inputs frequency independent of each other

• Any input can be designated as external frame/sync pulse of PPES (pulse per even second), 1PPS (Pulse per Second),

5PPS, 10PPS, 50Hz, 100Hz, 1 kHz, 2 kHz, 4kHz, and 8kHz associated with a selectable reference clock input

• Per-input programmable phase offset of up to ±1.638s in 1ps steps

▪ Reference monitors qualify/disqualify references depending on LOS, activity, frequency monitoring, and/or LOS input pins

• Loss of Signal (LOS) input pins (via GPIOs) can be assigned to any input clock reference

Specifications

| Attribute | Attribute value |

| ANSM-Part# | ANSM-8A34001E-000AJG |

| Category | Integrated Circuits (ICs) |

| Clock/Timing | |

| Clock Generators, PLLs, Frequency Synthesizers | |

| Mfr | Renesas Electronics Corporation |

| Series | - |

| Package | Tray |

| Product Status | Active |

| DigiKey Programmable | Not Verified |

| Type | Clock Synchronizer |

| PLL | Yes |

| Input | Clock |

| Output | CML, HCSL, HSTL, LVCMOS, LVDS, LVPECL, SSTL |

| Number of Circuits | 8 |

| Ratio - Input:Output | 0.341666667 |

| Differential - Input:Output | Yes/Yes |

| Frequency - Max | 1GHz |

| Divider/Multiplier | Yes/No |

| Voltage - Supply | 1.71V ~ 3.465V |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Mounting Type | Surface Mount |

| Package / Case | 144-TFBGA |

| Supplier Device Package | 144-CABGA (10x10) |

| Base Product Number | 8A34001 |

Actual product photos

Product Data Book:

For more product information, please download the PDF

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

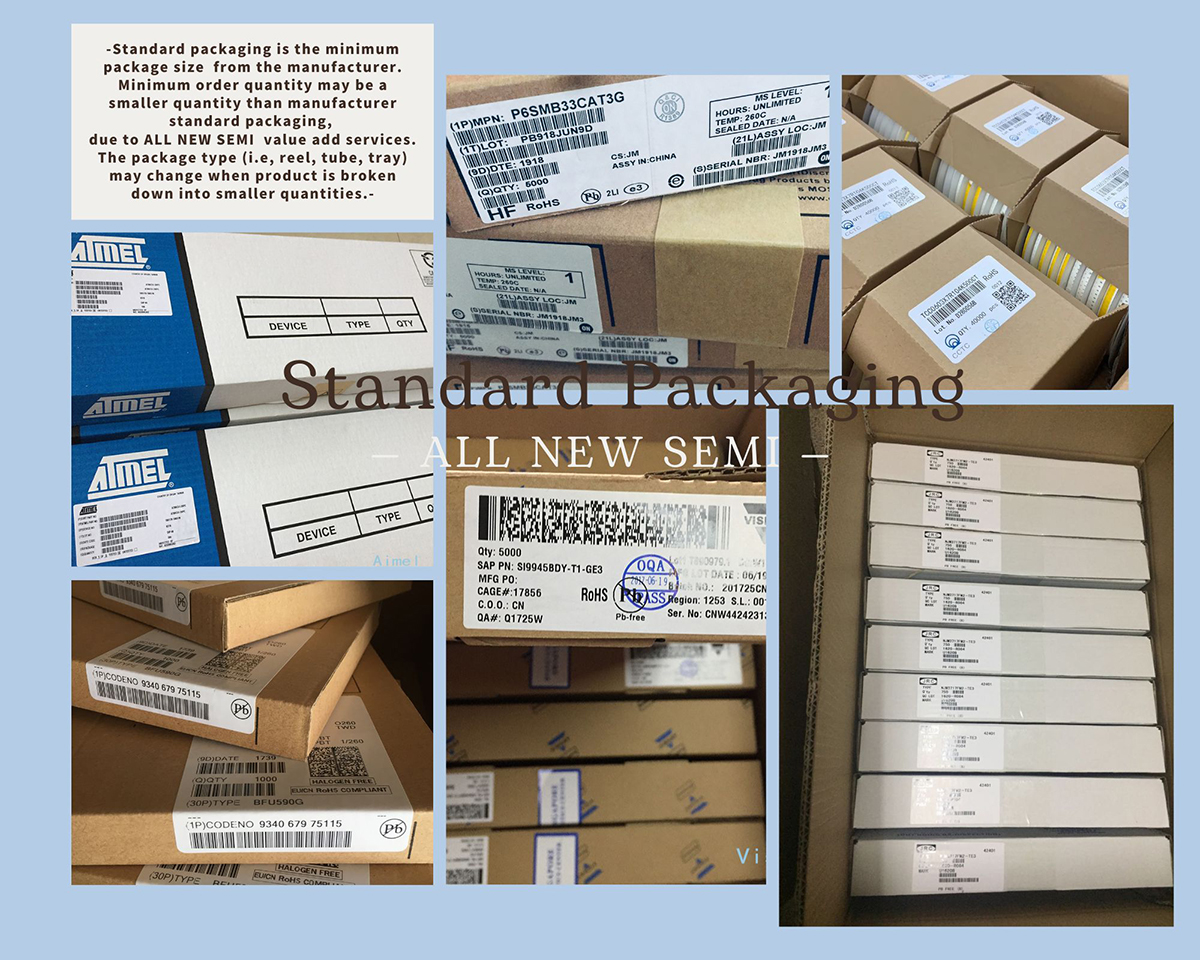

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |