Image shown is a representation only.

Exact specifications should be obtained from the product data sheet.

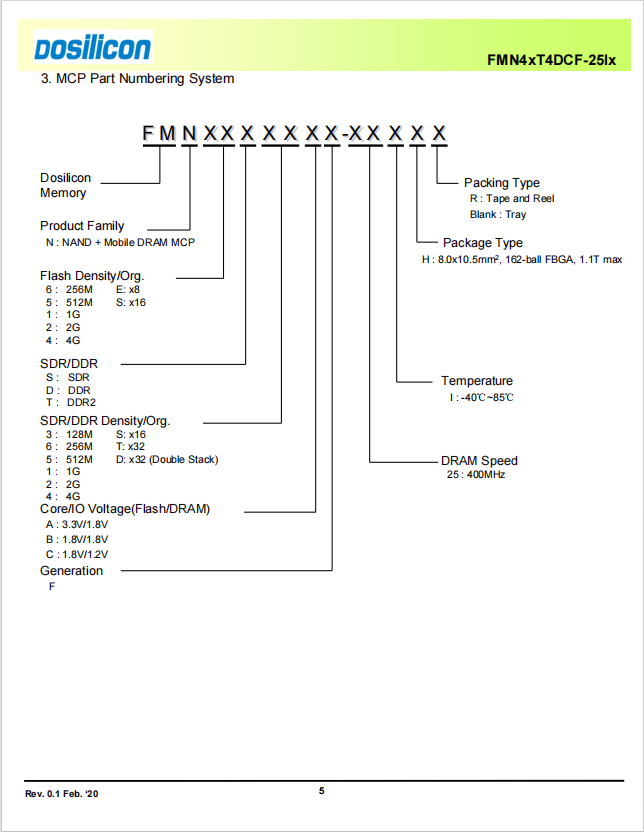

One stop electronic component supply Original FMN4ET4DCF-25IH Stacked Multi-Chip Product 1.8V NAND Flash Memory and Mobile DDR2

FMN4ET4DCF-25IH-Multiplexed, double data rate, command/address inputs;

commands entered on every CK edge

- Bidirectional/differential data strobe per byte of

data(DQS/DQS#).

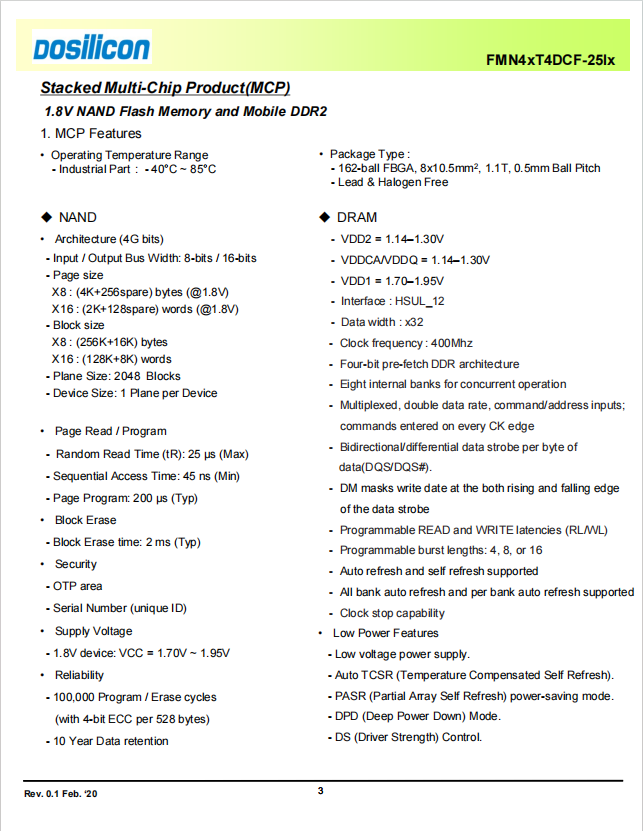

Product Features

1. MCP Features

• Operating Temperature Range

- Industrial Part : - 40°C ~ 85°C

• Package Type :

- 162-ball FBGA, 8x10.5mm2, 1.1T, 0.5mm Ball Pitch

- Lead & Halogen Free

NAND

• Architecture (4G bits)

- Input / Output Bus Width: 8-bits / 16-bits

- Page size

X8 : (4K+256spare) bytes (@1.8V)

X16 : (2K+128spare) words (@1.8V)

- Block size

X8 : (256K+16K) bytes

X16 : (128K+8K) words

- Plane Size: 2048 Blocks

- Device Size: 1 Plane per Device

• Page Read / Program

- Random Read Time (tR): 25 μs (Max)

- Sequential Access Time: 45 ns (Min)

- Page Program: 200 μs (Typ)

• Block Erase

- Block Erase time: 2 ms (Typ)

• Security

- OTP area

- Serial Number (unique ID)

• Supply Voltage

- 1.8V device: VCC = 1.70V ~ 1.95V

• Reliability

- 100,000 Program / Erase cycles

(with 4-bit ECC per 528 bytes)

- 10 Year Data retention

DRAM

- VDD2 = 1.14–1.30V

- VDDCA/VDDQ = 1.14–1.30V

- VDD1 = 1.70–1.95V

- Interface : HSUL_12

- Data width : x32

- Clock frequency : 400Mhz

- Four-bit pre-fetch DDR architecture

- Eight internal banks for concurrent operation

- Multiplexed, double data rate, command/address inputs;

commands entered on every CK edge

- Bidirectional/differential data strobe per byte of

data(DQS/DQS#).

- DM masks write date at the both rising and falling edge

of the data strobe

- Programmable READ and WRITE latencies (RL/WL)

- Programmable burst lengths: 4, 8, or 16

- Auto refresh and self refresh supported

- All bank auto refresh and per bank auto refresh supported

- Clock stop capability

• Low Power Features

- Low voltage power supply.

- Auto TCSR (Temperature Compensated Self Refresh).

- PASR (Partial Array Self Refresh) power-saving mode.

- DPD (Deep Power Down) Mode.

- DS (Driver Strength) Control.

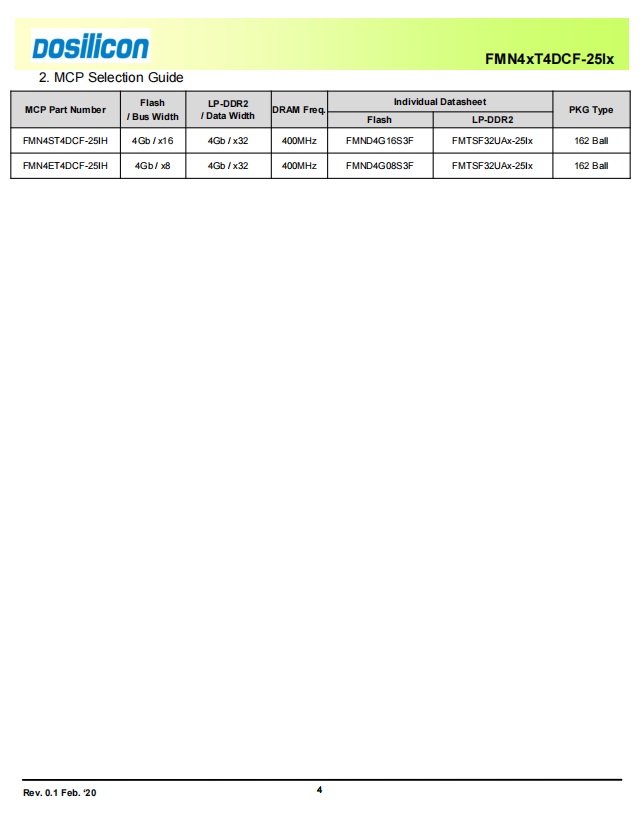

Specifications

| Attribute | Attribute value |

| ANSM-Part# | ANSM-FMN4ET4DCF-25IH |

| Type: | LPDDR2 |

| Manufactor | Dosilicon |

| DC | Standard |

| Describe | NEW |

| Supplier Device Packaging | FBGA162 |

| Package | TRAY |

| Density | 4Gb |

| Voltage (V) | 1.8 |

| Speed (MHz/CLK) | 400MHz |

| Temp.Range | -40℃~85℃ |

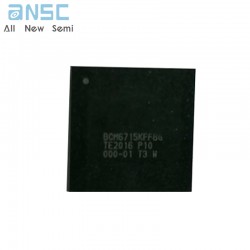

Actual product photos

Product Data Book:

For more product information, please download the PDF

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

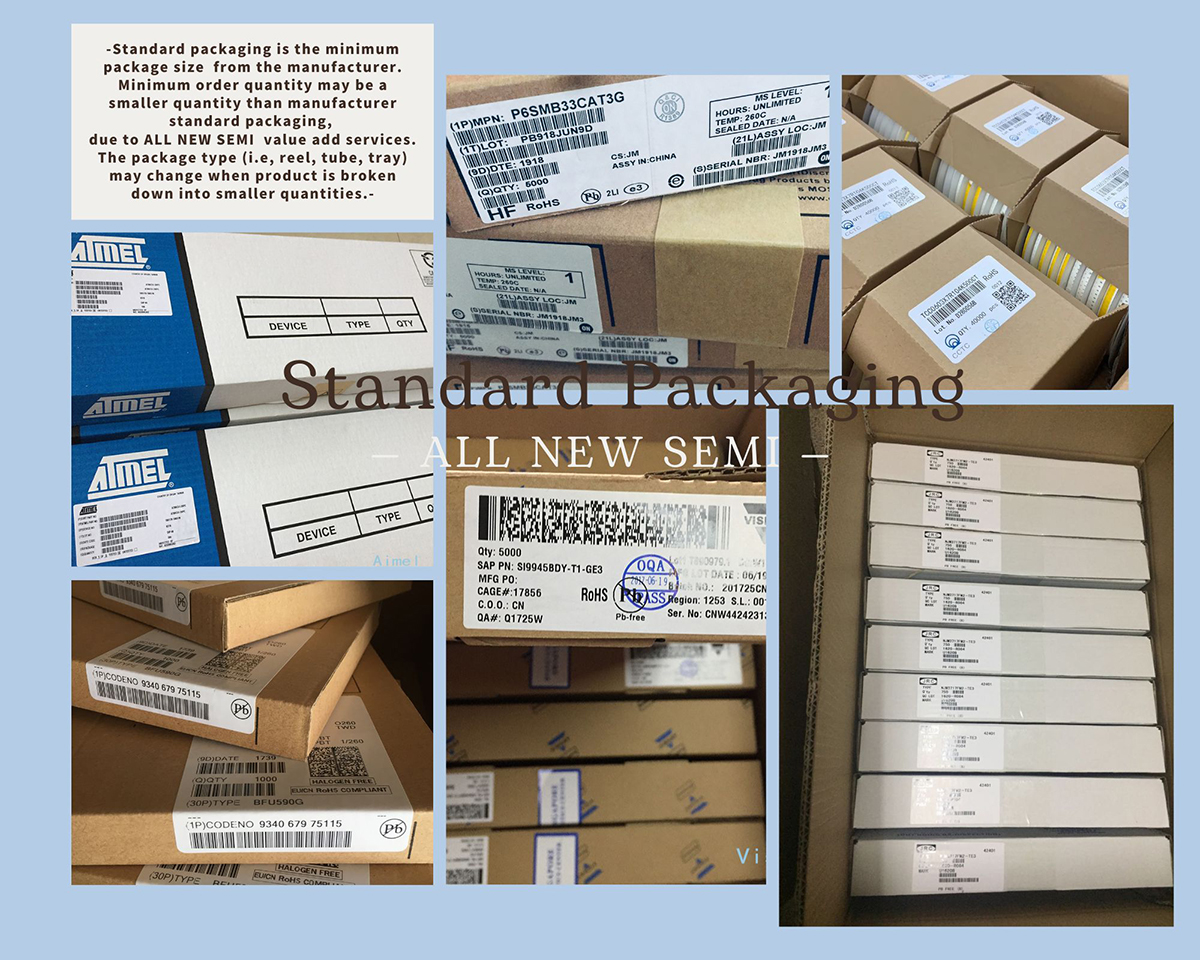

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |